#### **Doosan Heavy Industries & Construction**

# DOOSAN "DFLC-Q" Development

Class 1E FPGA-based Logic Controller for Nuclear Power Plants

> 12/04/2017 Jin-Young Lim

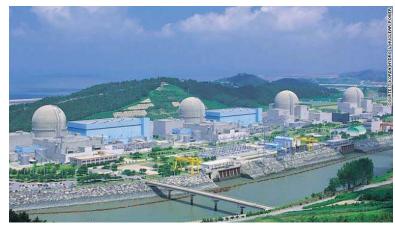

# South Korea & North Korea

• Nuclear Power ...

⇒ <u>"Dangerous" Bombs ...</u>

⇒ <u>"Safety" Plants !!!</u>

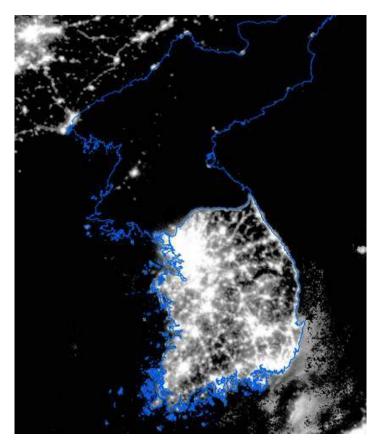

# South Korea & North Korea

## • Nuclear Power ...

Satellite View at Night...

Doosan Heavy Industries & Construction

# **Table of Contents**

## 1. Introduction

- . Technology for Digital I&C Solution

- . Background of Development FLC

## 2. "DFLC-Q"

- . Technology Choice of FPGA (Case-Study)

- . Overall Development Activities

- . Main Features & Architecture

## 3. Summary

# Background : Technology Trend

Analog System Vs. Digital System

**Doosan Heavy Industries & Construction**

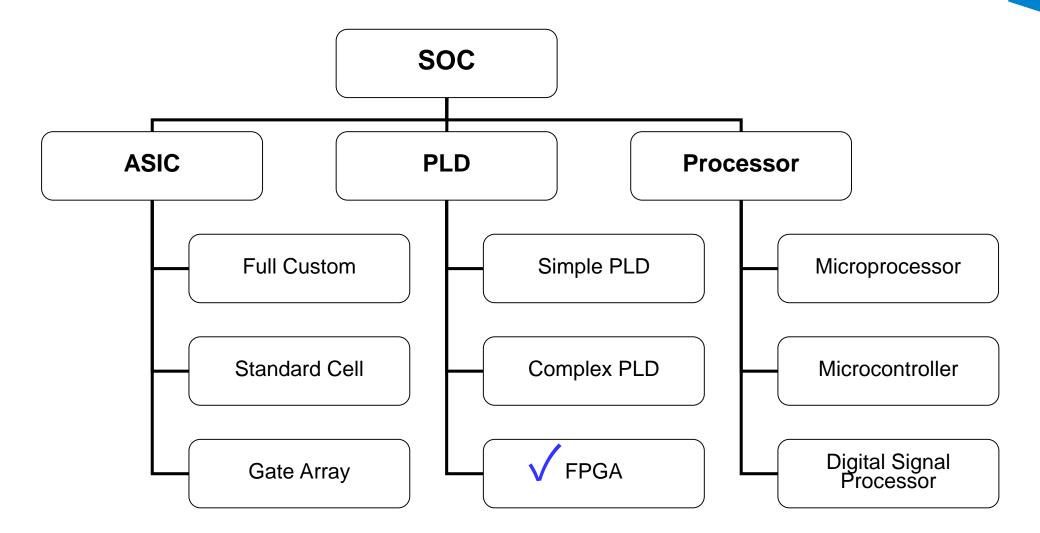

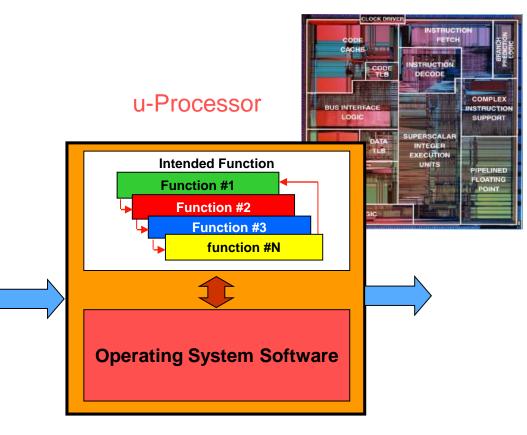

# Technology Choice for Digital I&C Design (1)

# Technology Choice for Digital I&C Design (2)

- Sequential Processing

- Complex Operating System

- Complex middle-ware

- Complex communications software

- Complex maintenance software

- Parallel Processing

- No Operating system

- Application logic is directly realized into hardware

- High degree of verifiability

- More deterministic feature

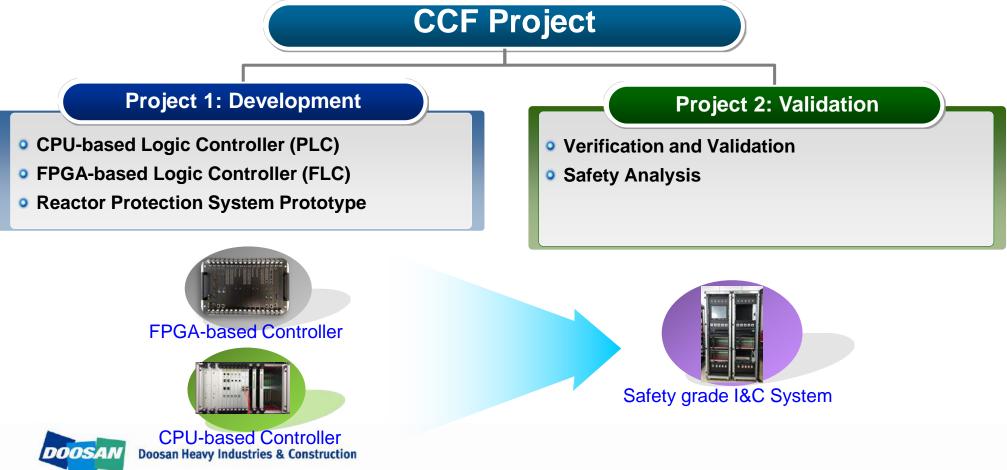

# CCF & SPV in Digital I&C system

## CCF (Common Cause Failure)

- Requirements are continuously being increased to make sure safety & reliability of NPP

- SPV: Single Point Vulnerability

- are continuously being removed to enhance the reliability of NPP

## Required to develop different platform

Launched "Development of safety I&C system and controller against CCF " by Korean R&D team

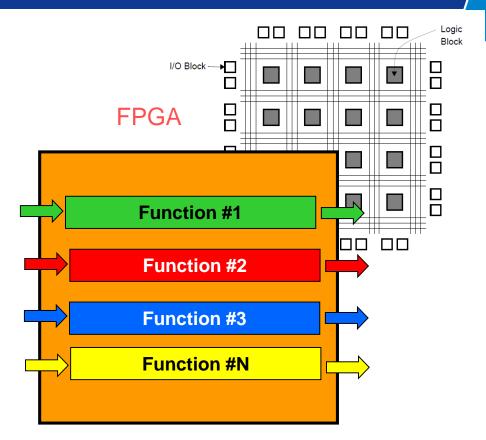

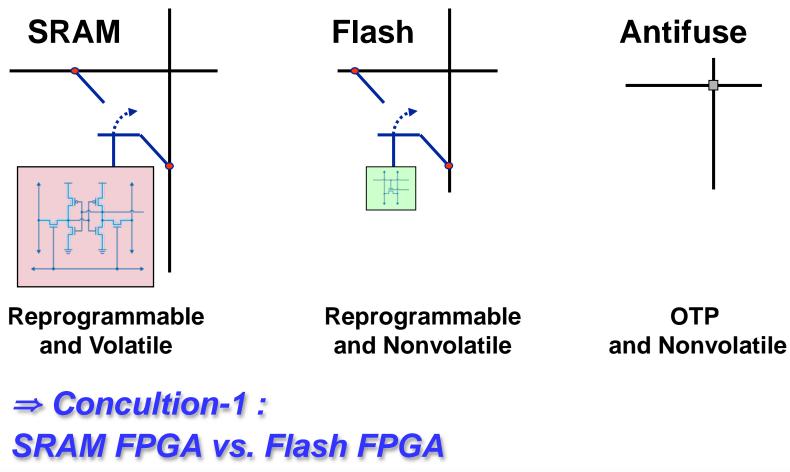

# **Digital I&C Solution against CCF**

## Different Platform of PPS will resolve the CCF Issues

- As is Class 1E Protection System

- To be Class 1E independent Protection System using different platform

- For example) FPGA based PPS and PLC based PPS are using the same time.

# **Table of Contents**

## **1. Introduction**

- . Technology for Digital I&C Solution

- . Background of Development FLC

## 2. "DFLC-Q"

- . Technology Choice of FPGA (Case-Study)

- . Overall Development Activities

- . Main Features & Architecture

## 3. Summary

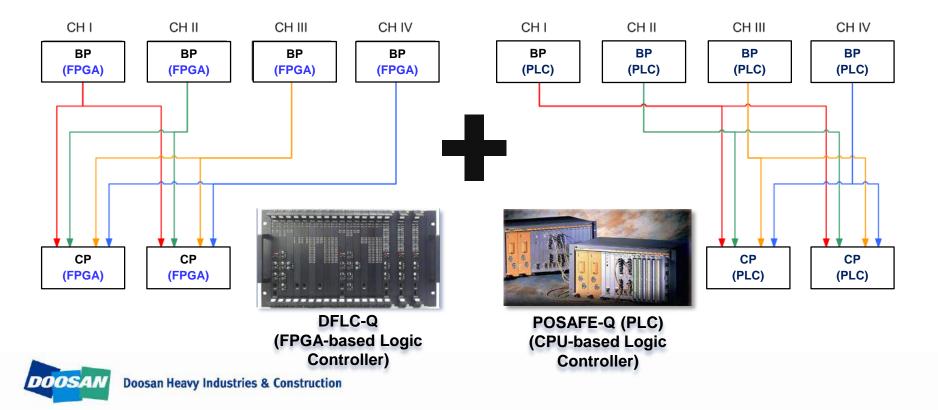

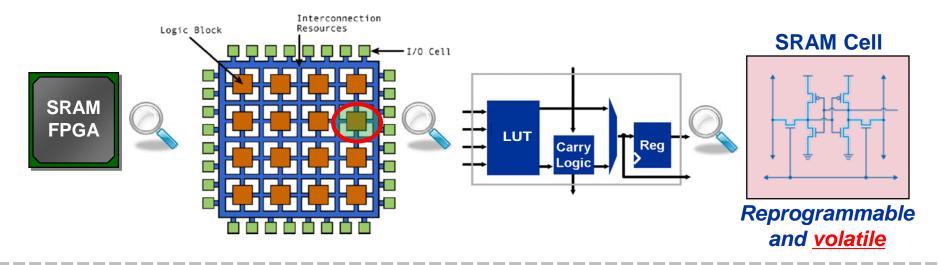

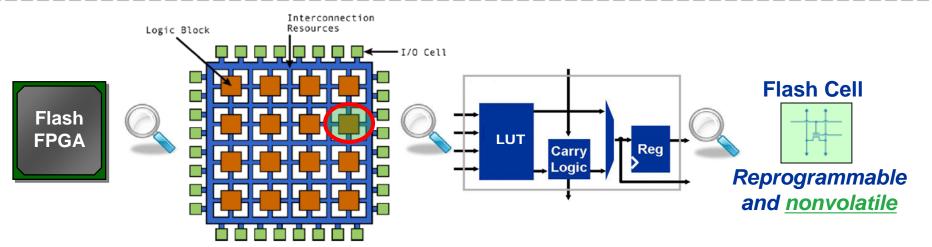

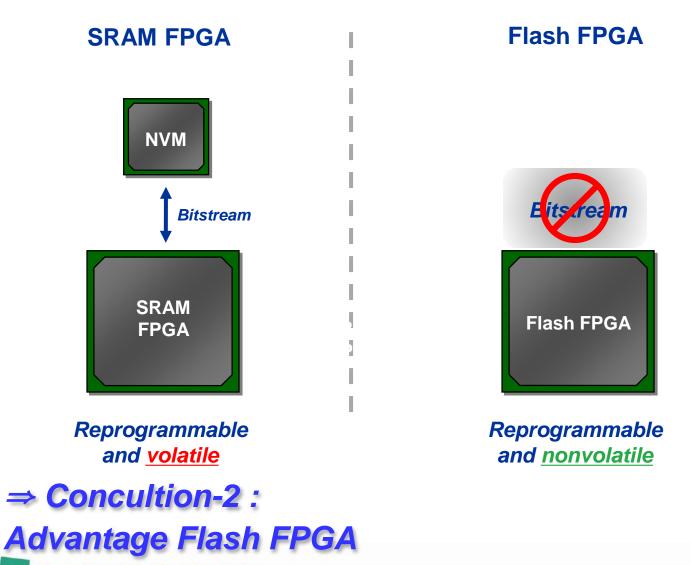

# **Technology Choice of FPGA**

FPGA Interconnection Technologies

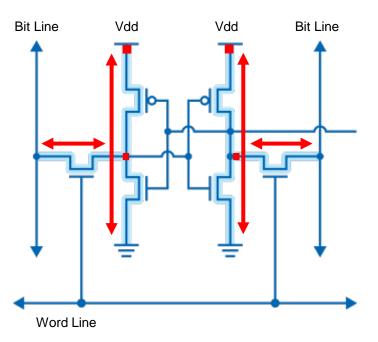

## Typical SRAM Cell

- High performance

- Millions of Configuration Cells

- Substantial Leakage per Cell

- High Static Current

- ⇒ Volatile

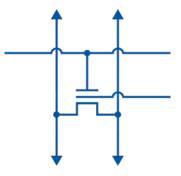

### Flash Cell

- Lower performance

- Lower Configuration Cells

- Lower leakage per cell

- Low Static Current

- ⇒ Non-Volatile

DOOSAN Doosan Heavy Industries & Construction

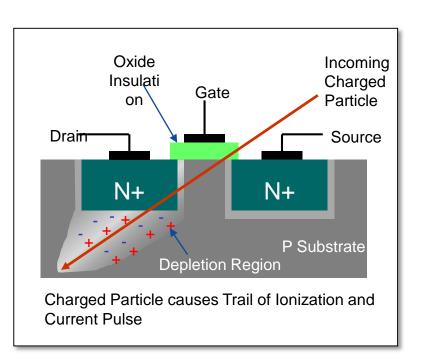

## • Radiation Effects in Semiconductors

- Charged particles (alphas, heavy ions, ...) cause momentary current pulses in CMOS ICs

- Data in memory cells and flip-flops can change

- Memory cells and flip-flops are not damaged

- Industry uses term "soft errors" to describe this process

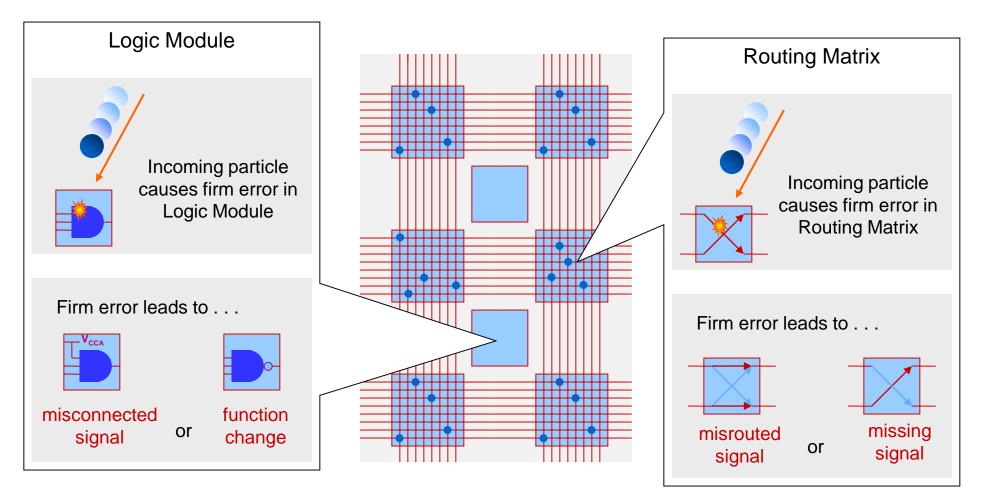

# **Cofiguration Upset in FPGAs**

How radiation causes SRAM FPGAS to malfunction

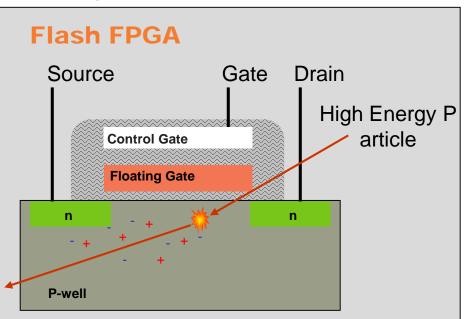

# Flash-based FPGAs – Immune to Configuration Upsets

- Absence of configuration upsets are why Flash-based FPGAs are the Industry Standard for space-flight applications

- not damaged

## ⇒ Concultion-3 : Advantage Flash FPGA

High energy particles (atmospheric neutrons, he avy ions in space) cannot generate sufficient cha rge to cause the floating gate to erroneously cha nge state

- True for current generation

- True for next generation

# **Table of Contents**

## **1. Introduction**

- . Technology for Digital I&C Solution

- . Background of Development FLC

## 2. "DFLC-Q"

- . Technology Choice of FPGA (Case-Study)

- . Overall Development Activities

- . Main Features & Architecture

## 3. Summary

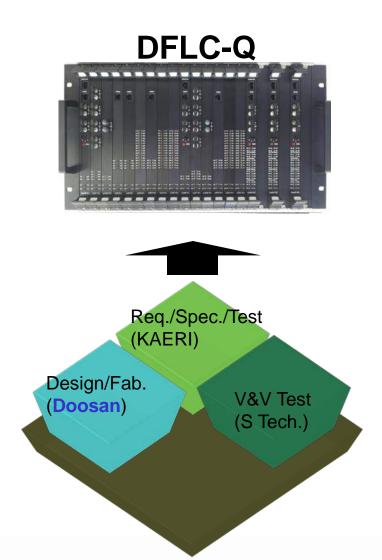

# Development of safety I&C and controller against CCF

## Korean I&C R&D Project

"Development of safety I&C system and controller against CCF" has been launched to improve the diversity of I&C system

# **Overall Activities for Development**

#### Phase 1 (2011 ~ 2013)

- Prototype Developing

- H/W & Logic Spec.

- H/W & Logic Design

- Functional Testing

- Performance Testing

- Simplified Qualification Testing

#### Phase 2 (2014 ~ 2016)

- End Product Developing

- H/W & Logic Redesign

- Functional Testing

- Performance Testing

- Qualification Testing

# **Table of Contents**

## **1. Introduction**

- . Technology for Digital I&C Solution

- . Background of Development FLC

## 2. "DFLC-Q"

- . Technology Choice of FPGA (Case-Study)

- . Overall Development Activities

- . Main Features & Architecture

## 3. Summary

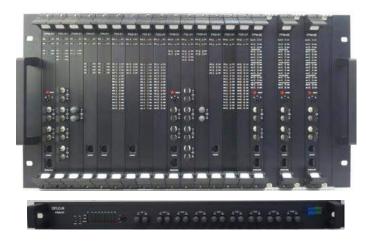

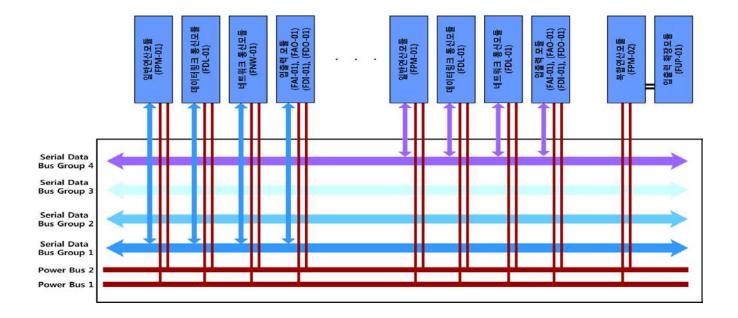

# DFLC-Q [ DOOSAN FPGA-based Logic Controller for Class 1E ]

## • Subrack :

- 19-inch Standardization (482.6 x 281.35 x 294mm )

- Total 21 Slots per Subrack

- Redundant power bus

- Supported 4 system bus groups

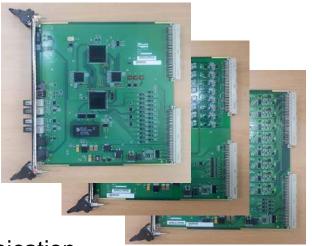

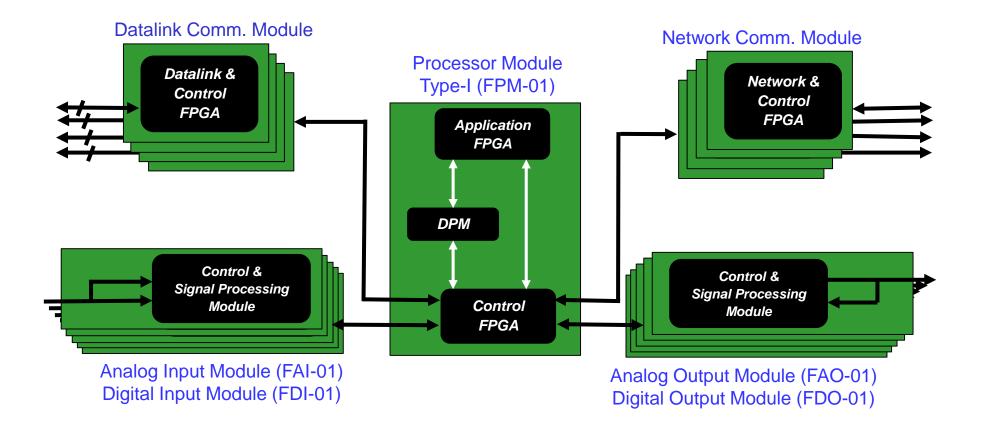

## Module Type :

- Processor Module (Type-I, Type-II)

- Analog Input Module / Analog Output Module

- Digital Input Module / Analog Output Module

- Communication Module

- Datalink Module for Safety Communication

- Network / Switch Module for Information Communication

# **Overall Hardware Specification**

| Module Type          | Item                                          | Specification                                             | Description                                        |

|----------------------|-----------------------------------------------|-----------------------------------------------------------|----------------------------------------------------|

| Processor            | Туре-І                                        | Control & Application Logic                               | Embedded Datalink Comm. ports (2-Ch)               |

| Module               | Туре-ІІ                                       | Control & Application Logic<br>+ Analog / Digital I/O Ch. | Embedded I/O Channel<br>(Support Extension Module) |

| Analog I/O<br>Module | Range                                         | 0V~10V, 4mA~20mA                                          | 8-Ch (Current / Voltage)                           |

|                      | Accuracy                                      | ±0.1%                                                     | 18-bit AD / 16-bit DA                              |

|                      | Update Time                                   | Min. 5 msec                                               | w/ PM Scantime                                     |

| Digital I/O          | Range                                         | 0V ~ 24V                                                  | 32-Ch                                              |

| Module               | Update Time                                   | Min. 5 msec                                               | w/ PM Scantime                                     |

| Datalink Comm.       | Speed                                         | 10-Mbps                                                   | 4-Ch per Module<br>(Separated Tx / Rx port)        |

| Module               | Protocol                                      | Based on RS-485                                           |                                                    |

| Network Comm. +      | nm. + Speed 2010bps / 64-hode (Separated Tx / | 1-Ch per Module<br>(Separated Tx / Rx port)               |                                                    |

| Netwok Switch Module | Protocol                                      | TDMA                                                      |                                                    |

# DFLC-Q: System Bus Architecture

- 1-Subrack :

- "Supported 4 System-Bus-Group

- ⇒ Support 4 independent sub-system per subrack

# DFLC-Q: System Diagnosis

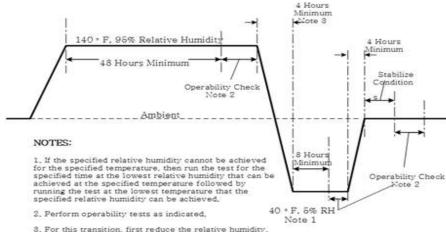

# Equipment Qualification Test(1)

## Environmental qualification (IEEE Std. 323-2003, Reg. Guide 1.209)

then reduce the temperature. This is required to maintain a non-condensing atmosphere.

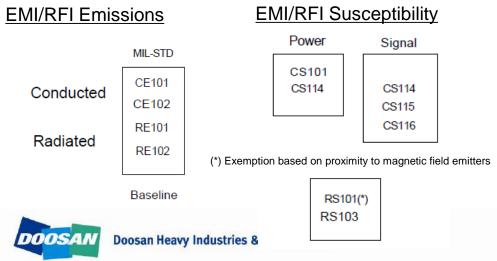

## EMI/RFI (Reg. Guide 1.180-2003, IEC 61000-4-2-2008)

# Equipment Qualification Test(1)

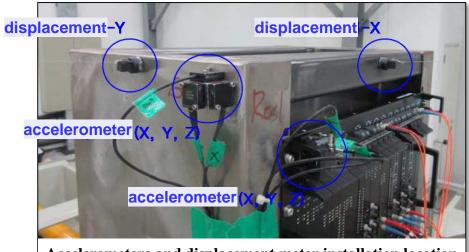

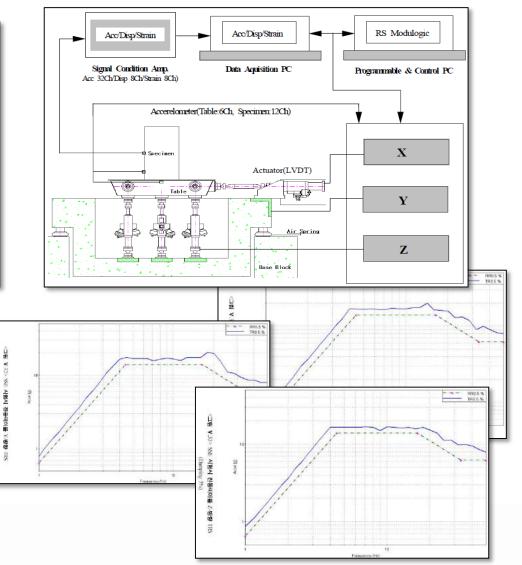

• Seismic Testing (IEEE Std. 344-2004, Reg. Guide 1.110)

Accelerometers and displacement meter installation location

Allowed during seismic testing standards

| No | Signal type     | Tolerance                  | Etc.      |

|----|-----------------|----------------------------|-----------|

| 1  | Analog Voltage  | 5 V ± 0.14%                | 4 Channel |

| 2  | Analog Current  | $12 \text{ mA} \pm 0.14\%$ | 1 channel |

| 3  | Digital Voltage | 22 ~ 24 VDC                | 5 channel |

# **Overall development life cycle(1)**

| IEC 62566 Section 9                                        | C 62566 Section 0 Application Notes                                                                            |                                                                                         | IEC 62566 : Development life-cycle of HPD |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------|--|

| HPD Verification                                           | Application Notes                                                                                              | HPD requirement                                                                         | HPD aspects of                            |  |

| 9.1 General                                                | Independent V&V team                                                                                           | specification                                                                           | system validation                         |  |

| 9.2 Verification plan                                      | <ul> <li>Software V&amp;V plan in the concept phase</li> </ul>                                                 | Verification                                                                            |                                           |  |

| 9.3 Verification of the use of the pre-<br>developed items | Original software                                                                                              | HPD design<br>specificationHPD aspects of<br>system integrationVerificationVerification |                                           |  |

| 9.4 Verification of the design and implementation          | <ul> <li>SRS, SDD document evaluation</li> </ul>                                                               |                                                                                         |                                           |  |

| 9.5 Test-benches                                           | <ul> <li>Test-benches to fulfil requirement and path<br/>coverage</li> </ul>                                   |                                                                                         |                                           |  |

| 9.6 Test Coverage                                          | <ul> <li>Path/Branch coverage for Component Test</li> <li>Requirement coverage for Integration Test</li> </ul> |                                                                                         | HPD implementation                        |  |

| Day 2 Wadwarda                                             | Robaviaral cimulation using tast honobas                                                                       |                                                                                         | \/:C!                                     |  |

| Duy 5 – w eunesuuy                                         | <i>v, 6 December 2017</i>                                                                                      |                                                                                         |                                           |  |

| Time                                                       | Event                                                                                                          |                                                                                         | Speaker                                   |  |

| Technical Session on De                                    | esign and Testing                                                                                              | Chai                                                                                    | r: Gyula Mach                             |  |

| 09.00 - 9.30                                               | tation 10: Verification and Validat<br>Logic Controller                                                        | Jangyeol Kim, KAERI                                                                     |                                           |  |

|                                                            | tries & Construction                                                                                           | Device                                                                                  |                                           |  |

# Summary of DFLC-Q Development

- Against CCF and SPV issues:

- Using Different platform is the one of the solution

- Proposed both FPGA-based and CPU-based Logic Controller

- > Developed both system in the past project

- Developed DFLC-Q by DOOSAN

- Based on Flash-based FPGAs

- The Next...

- > Processing to certify DFLC-Q as a Safety-Grade Digital I&C System

# Q & A