#### **Doosan Heavy Industries & Construction**

# Doosan Practice of V&V and Testing in FPGA Development Process

Oct 16, 2015 Shanghai, China

#### **1. Introduction**

- . V&V in FPGA Development Process

- : NUREG/CR-7006, IEC62566

### 2. V&V and Testing

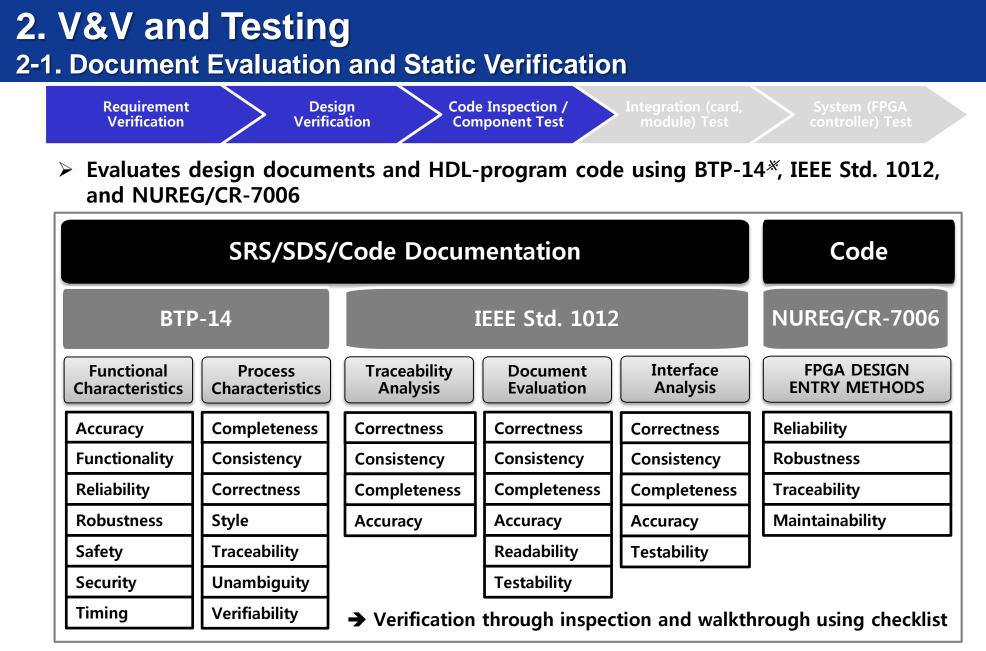

- . Document Evaluation and Static Verification

- . Component Test

- . Integration Test

- . System Test

### **1. Introduction**

- . V&V in FPGA Development Process

- : NUREG/CR-7006, IEC62566

- 2. V&V and Testing

- . Document Evaluation and Static Verification

- . Component Test

- . Integration Test

- . System Test

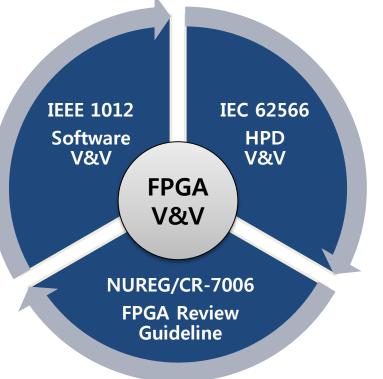

# **I. Introduction** 1-1. V&V in FPGA Development Process

> FPGA has mixed characteristics of hardware and software

#### > FPGA V&V is hard to be achieved with IEEE Std. 1012 (a basis for NPP software V&V)

- [NUREG/CR-7006] IEEE-1002-2004 is a software-only standard, and it can not be directly applied to V&V process for FPGA-based systems. Even though the top level V&V processes and underlying activities are generic and can be used for FPGAs, the low level tasks are software specific, and not directly applicable to FPGAs.

- → Harmonized existing FGPA standards and technologies into IEEE Std. 1012-based SDLC (Software Development Life Cycle)

- **IEEE Std. 1012 :** Standard for Software Verification and Validation

- NUREG/CR-6007 : Review Guidelines for Field-Programmable Gate Arrays in Nuclear Power Plant Safety Systems

- IEC 62566 Nuclear power plants Instrumentation and control important to safety – Development of HDL-programmed integrated circuits for systems performing category A functions

# I. Introduction

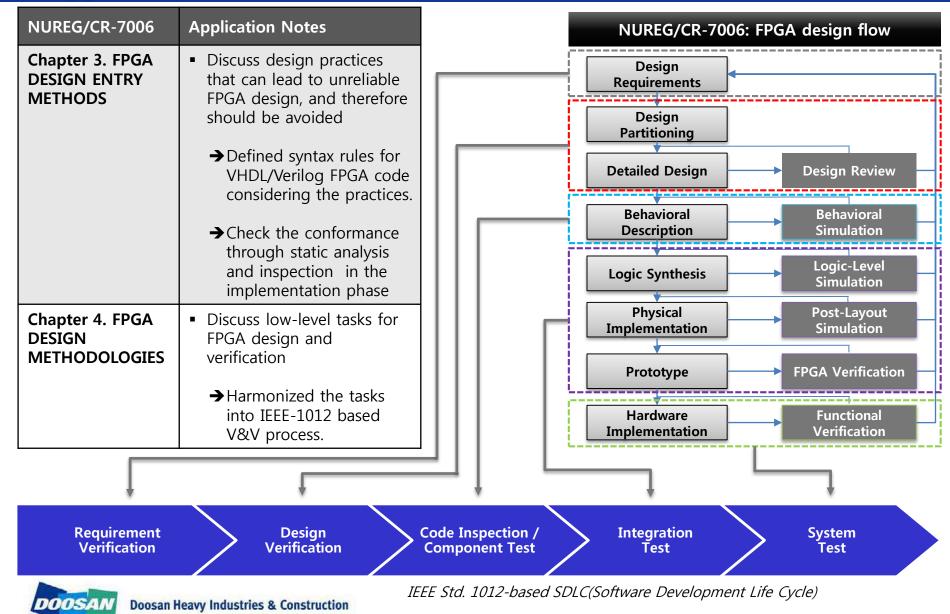

#### 1-2. Application of NUREG/CR-7006 Review Guidelines for FPGA in NPPS

## **I. Introduction** 1-3. Application of IEC 62566 : HPD% Verification

| Application Notes                                                                                                      | IEC 62566 : Dev                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Independent V&amp;V team</li> </ul>                                                                           | HPD requirement                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>Software V&amp;V plan in the<br/>concept phase</li> </ul>                                                     | specification<br>Verification                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Original software</li> </ul>                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>SRS, SDD document evaluation</li> </ul>                                                                       | HPD design<br>specification                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>Test-benches to fulfil requirement<br/>and path coverage</li> </ul>                                           | Verificatio                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>Path/Branch coverage for<br/>Component Test</li> <li>Requirement coverage for<br/>Integration Test</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>Behavioral simulation using test benches</li> <li>Timing simulation</li> </ul>                                |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>NUREG/CR-7006 based type and<br/>syntax checking</li> </ul>                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Design<br>Verification                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                        | <ul> <li>Independent V&amp;V team</li> <li>Software V&amp;V plan in the concept phase</li> <li>Original software</li> <li>SRS, SDD document evaluation</li> <li>Test-benches to fulfil requirement and path coverage for Component Test</li> <li>Path/Branch coverage for Integration Test</li> <li>Behavioral simulation using test benches</li> <li>Timing simulation</li> <li>NUREG/CR-7006 based type and syntax checking</li> </ul> |

**Doosan Heavy Industries & Construction**

DOOSAN

*※ HPD : HDL-Programmed Device*

#### **1. Introduction**

- . V&V in FPGA Development Process

- : NUREG/CR-7006, IEC62566

## 2. V&V and Testing

- . Document Evaluation and Static Verification: V&V

- . Component Test

- . Integration Test

- . System Test

DOOSAN

X USNRC-0800 Standard Review Plan: Chapter 7. Instrumentation and Controls BTP-14

**Doosan Heavy Industries & Construction**

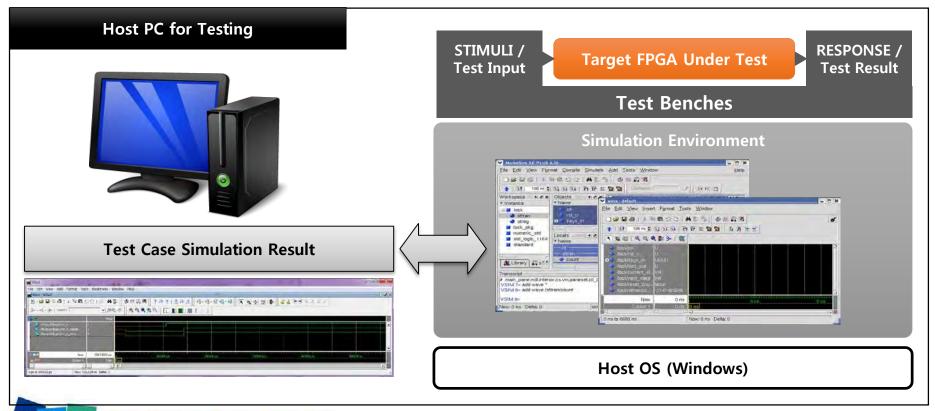

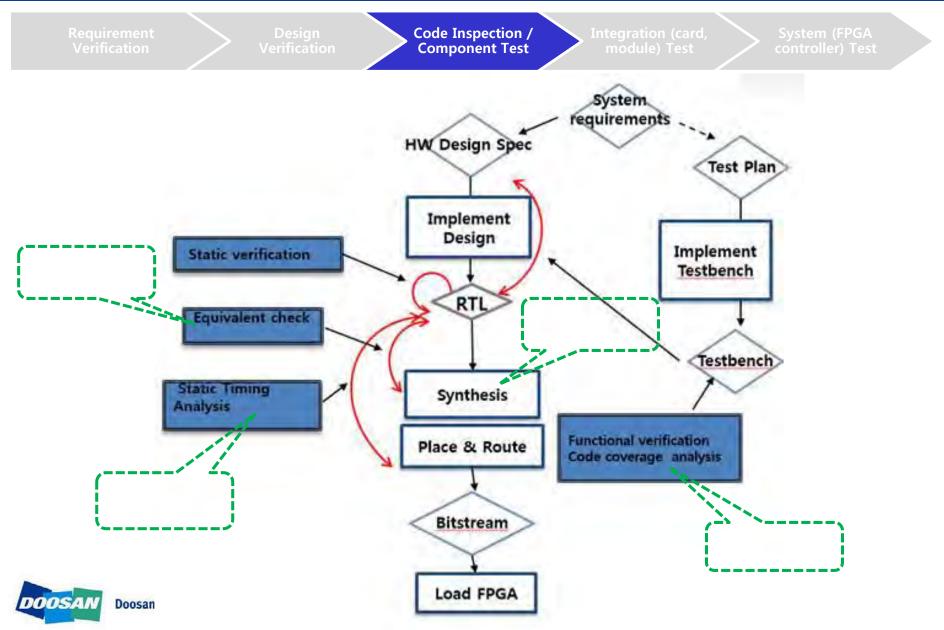

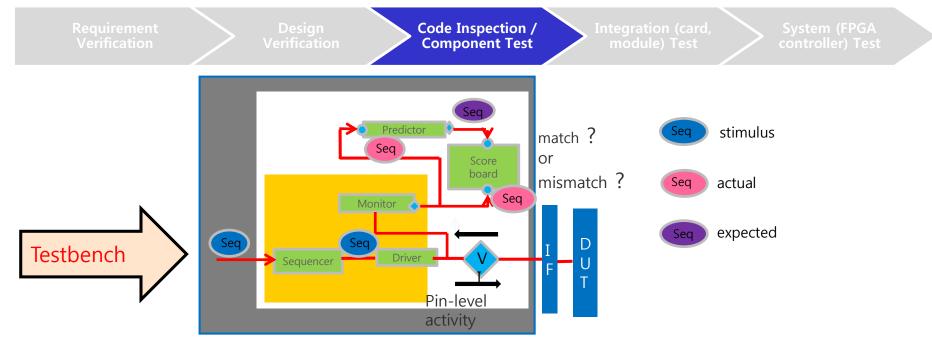

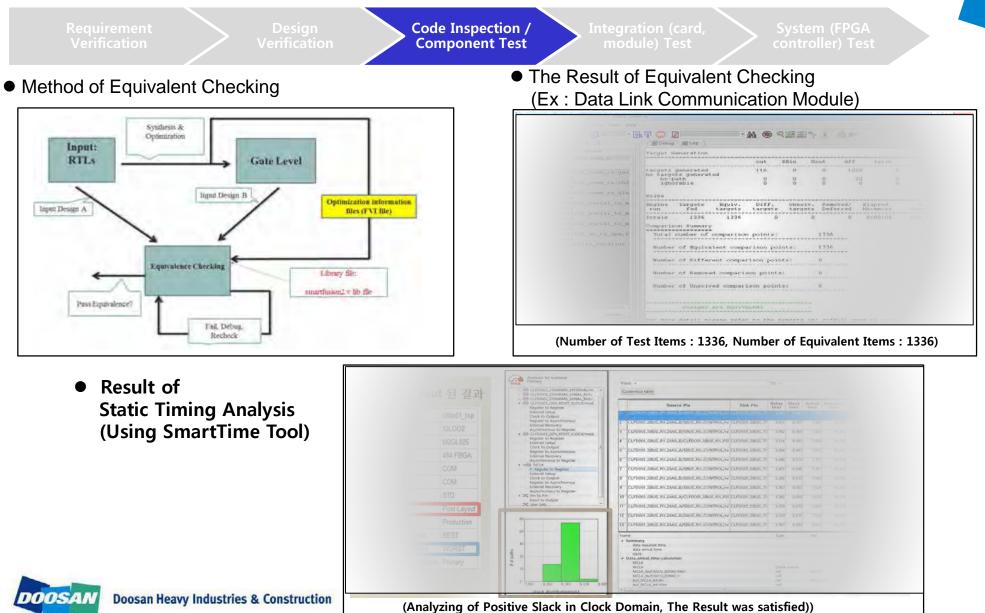

#### 2. V&V and Testing:Micro-semi(Libero) 2-2. Component Test Requirement Verification Design Verification Question Code Inspection / Integration (card, module) Test

- > Behavior/timing simulation was performed on RTL/HDL code

- > Test criteria : Path coverage, Requirement coverage

- Test environment : Host PC-based Simulation Environment

OOSAN

# 2. V&V and Testing 2-2. Component Test

# 2. V&V and Testing 2-2. Component Test

• The Result of Functional Test

| $\bullet$ | The | Result | of | Code | Coverage | Analysis |

|-----------|-----|--------|----|------|----------|----------|

|-----------|-----|--------|----|------|----------|----------|

93.7%

50.0% 95.1%

80.4%

Stnt count Strits hit Strits Strit % Strit graph Branch Branch B

1 97.89

1 80%

0 100% 0 100%

0 100%

5 0 100% 5 0 100%

5 0 100%

5 0 100% 5 5 0 100% 12 12

108 107

108 107

12 12 12 12

12 12

12 12 12 12

12 12

12 11 12 12

63 62 1 98.4%

45 44

fotal coverage

| >1 | SIGNAL          | 11  | status | 11  | value |       | expt | 11   | p/op |       | SWR |      |  |

|----|-----------------|-----|--------|-----|-------|-------|------|------|------|-------|-----|------|--|

| >1 | reset           | 11  | input  | 11  | 1     | 11    | n/e  | 11   | n/a  | 11    | 15  | 1.   |  |

| >1 | SEL_SHUS        | 11  | Input  | 11  | 1     | 1.1   | ts/e | 11   | n/a  | 1.1   | 2.5 |      |  |

| >1 | SLOT_POS        | 11  | inpur  | 11  | 0     | 11    | n/e  | 11   | n/a  | 11    | 15  | 1    |  |

| >1 | SRXD            | 1.1 | input  | 11  | 1111  | 11.   | T1/8 | 28.  | n/e  | 1.1   | 2.5 | 1.12 |  |

| >1 | id_module       | 11  | input  | 1.1 | 4601  | 11    | n/#  | 1.1  | n/a  | 13    | 15  | 1    |  |

| >1 | seel_this       | 1.1 | output |     | 0     | 01.6  | 0    |      | Pass | 11    | 15  | 1.   |  |

| 21 | err sel bus     | 11  | output | 3.1 | 0     | 1.1   | 0    | 8.8  | Pass | 11    | 3.5 | 1.12 |  |

| >1 | err_proc        | 11  | output | 4.4 | 0     | 11    | 0    | 1.1  | Pazz | 11    | 15  | 12   |  |

| >1 | err_Hrx         | 1.1 | output | 1.1 | 0     | 1.1   | 0    | 11   | Page | 11    | 25  | 1    |  |

| >1 | err_tx_scan     | 1.1 | output | 1.1 | 0     | 1.1.  | 0    | 4.2  | Pans | 1.1   | 1.5 | 1    |  |

| >1 | norm_op         | 1.1 | output | 1.1 | 0     | 11    | 0    | 1.1  | Pass | 1.1   | 15  | 1.1  |  |

| 21 | clr_erret       | 1.1 | output | 11  | 0     | 08.40 | 0    | 11   | Pass | 11    | 15  | 1    |  |

| >1 | en and set      | 11  | output | 11  | 0     | 11    | 0    | 1.1  | Pazz | 11    | 15  | 1    |  |

| >1 | set_scan_time   | 3.3 | output | 11  | fffe  | 11    | fffe | 1.6  | Pass | . 4 3 | 15  | T.   |  |

| >1 | set_en_tx_diag  | 11  | output | 11. | 0     | 1.1   | 0    | 11   | Pass | 1.1   | 3.5 |      |  |

| >1 | set_en_tx_ch    | 11  | output | 11  | 0     | 11.   | Ø    | 1.1  | Pass | 1.8   | 15  | 1.   |  |

| >1 | set_en_rx_diag  | 11  | output | 2.2 | 0     | 11    | 0    | 1.4  | Pass | 11    | 15  | 1    |  |

| >1 | set_en_rx_ch    | 11  | output | 1.1 | 0     | 11    | 0    | 1.1  | Pass | 11    | 25  | 1    |  |

| >1 | set_tx_sadr0-3  | 11  | eutput | 11  | ffff  | 11    | tttt | 1.4  | Pass | 1.1   | 15  | 1    |  |

| >1 | set tx madr0-3  | TT. | output | 11  | 2222  |       | 2222 | 4.15 | Pass | 11    | 15  | E.   |  |

| >1 | set_tx_dlen0-3  | 1.1 | output | 11  | 00    | 11    | 00   | 1.1  | Pass | 11    | 25  | 12   |  |

| >1 | set_rx_scant0+3 | 1.1 | output | 1.1 | itte  | 11    | fffe | 11   | Pass | 11    | 15  | 10   |  |

| >1 | set_ix_sadr0-3  | 11  | output | 11  | ette  | 11    | 2222 | 14   | Pess | 11    | \$5 | E    |  |

| >1 | set_rs_medr0-3  | 11  | nutput | 11  | 1111  | 11    | EFFE | 1.1  | Pass | 1.1   | 15  | 1    |  |

| >1 | set_rx_dlen0-3  | 11  | output | 3.8 | ea    | 11    | 80   | 1.1  | Fezz | 1.1   | \$5 | - F  |  |

| >1 | sta_op_dount    | 11  | output | 3.1 | 0     | 11    | 0    | 1.1  | Pass | 1.1   | 15  | - E  |  |

| >1 | drdy_ts_dpm     | 1.5 | output | 3.1 | 0     | 11    | 0    | 4.4. | Pozz | 4.1   | 2.5 | 1    |  |

(value : actual I/O, expt: expected value, p/np : True/False

# 2. V&V and Testing:detail output example 2-2. Component Test

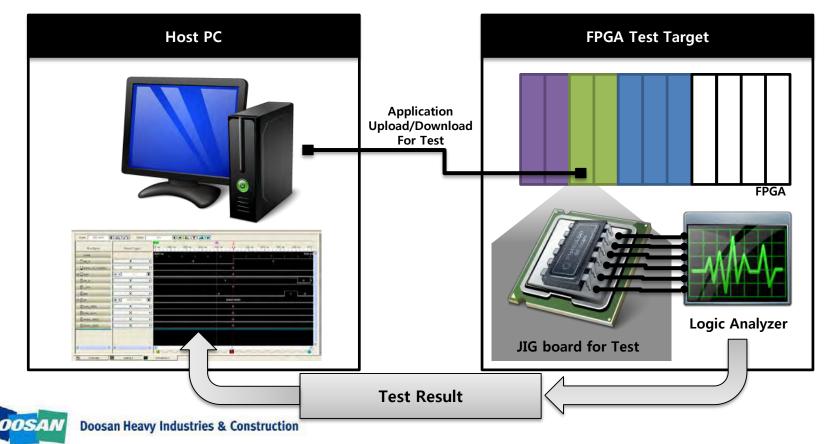

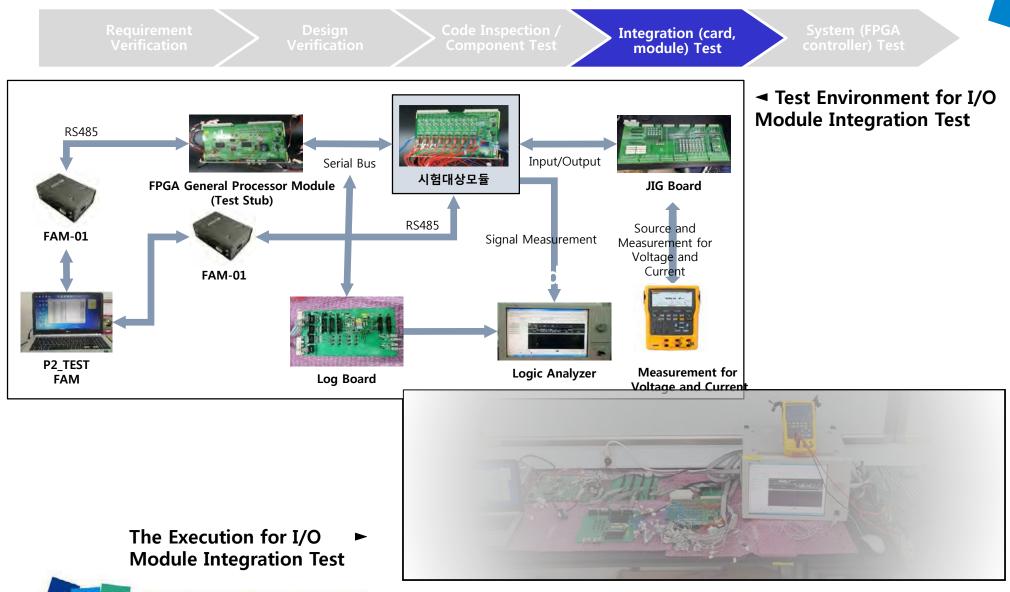

## 2. V&V and Testing 2-3. Integration Test

- > FPGA verification using hardware signal triggering and monitoring

- > Test criteria : Requirement coverage

- > Test environment : Jig board and signal jumpers for monitoring

# 2. V&V and Testing 2-3. Integration Test

10SAL

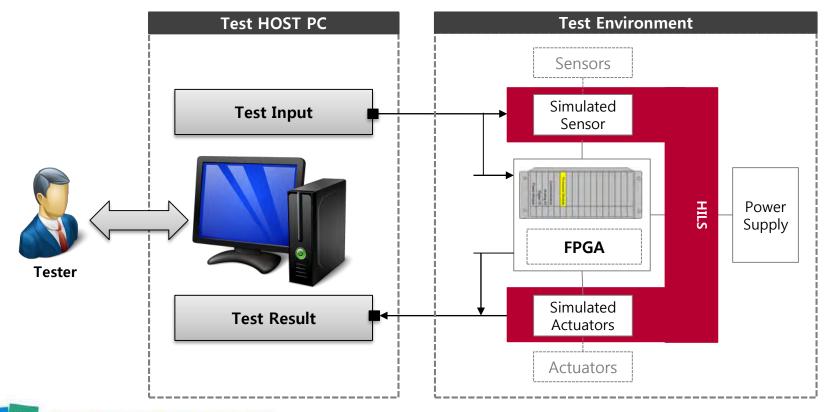

- > Validated by Hardware-in-the-loop simulation

- > Test criteria : Requirement coverage

- > Test environment : Hardware-in-the-loop simulation environment

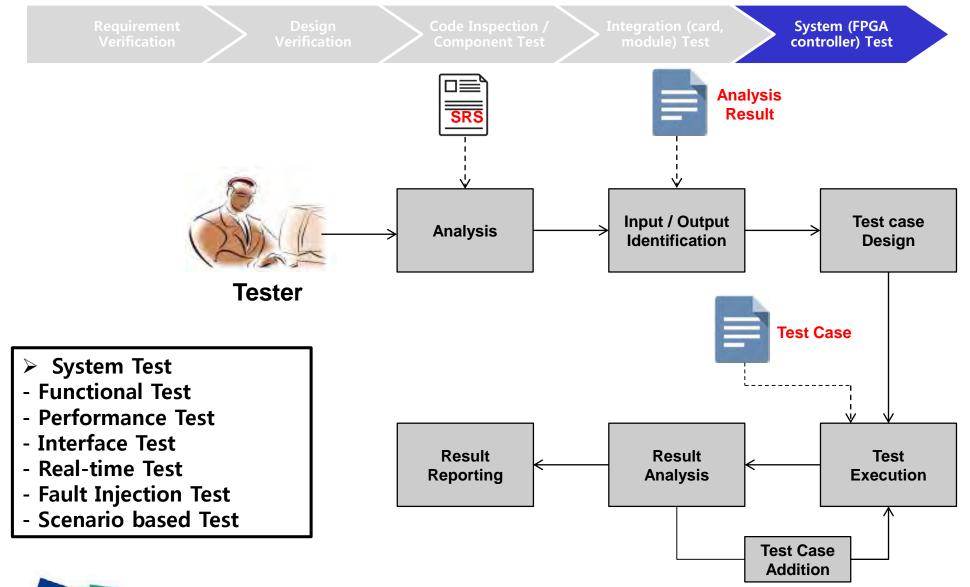

# 2. V&V and Testing 2-4. System Test

# 2. V&V and Testing 2-4. System Test

Requirement Verification

erification

ode Inspection / omponent Test Integration (card, module) Test

System (FPGA controller) Test

- 1. Platform Qualification

- Y=aX Linear Function : Full Range Test (10,000)

- 2. Manual Test before Automatic Testing

- Fluke 754, Graphic Record

- 3. I/O Combination Test (AI-AO, DI-DO, DI-FDL-GP-F D L-DO)

- 4. Scenario based automatic testing after Satisfying of 1,2 and 3 conditions

- 1) Functional (Triangle Wave : 0-Increment-peack-decrement-0): 10,000 Test Case

- 2) Performance (Input:25ms –GP –output:50ms : Closed Loop BACK PASS/FAIL )

- 3) Real-time (2ms~1000ms :25ms, 50ms, 500ms etc.)

- 4) Accuracy : 0.01% tolerance

- 5. Analysis of Test Result

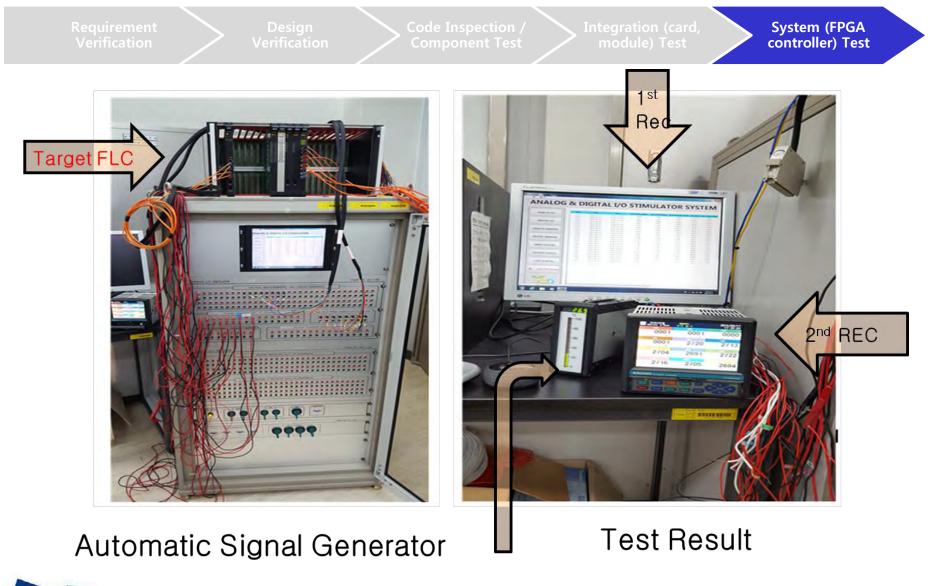

# 2. V&V and Testing 2-4. System Test

TODSAL

#### **1. Introduction**

- . V&V in FPGA Development Process

- : NUREG/CR-7006, IEC62566

### 2. V&V and Testing

- . Document Evaluation and Static Verification

- . Component Test

- . Integration Test

- . System Test

- Let's share practice & ideas for peaceful use of Nuclear Energy ----- Objective/Mission of IAEA, President D. Eisenhower

- To lead Nuclear Renaissance again

# hank you for listening

**DOOSAN Heavy Industries & Construction**

**Doosan Heavy Industries & Construction**